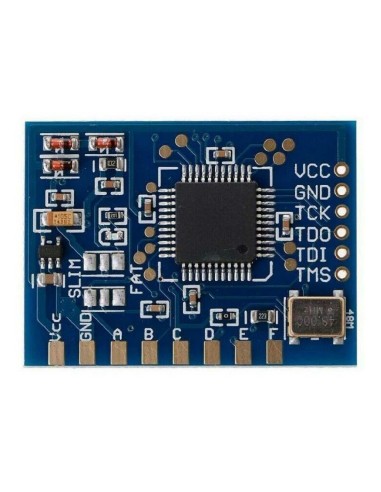

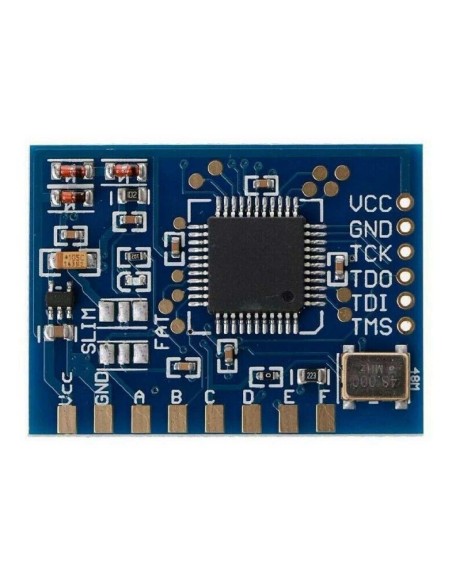

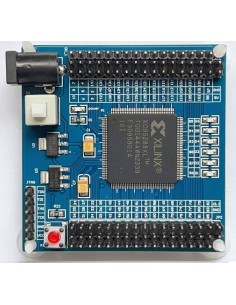

O Matrix Glitcher CPLD é uma placa baseada no Xilinx XC2C64A (CoolRunner‑II CPLD), usada principalmente em experimentos de lógica digital e aplicações de glitching/controladores. O chip oferece 64 macrocélulas, operação em baixa potência e suporte a múltiplos níveis de I/O (1,5–3,3 V).

🔹 Dispositivo principal: Xilinx XC2C64A

- Família: CoolRunner‑II CPLD.

- Tecnologia: 0,18 µm CMOS, otimizada para baixo consumo.

- Macrocélulas: 64 (aprox. 1.600 portas lógicas equivalentes).

- Arquitetura:

- 4 blocos de função interconectados por Advanced Interconnect Matrix (AIM).

- Cada bloco com 16 macrocélulas configuráveis.

- Memória de configuração: não volátil, baseada em EEPROM.

- Velocidade: atrasos pin‑to‑pin de até 4,6 ns.

- Consumo: corrente de repouso tão baixa quanto 15 µA.

- I/O:

- Até 64 pinos de entrada/saída (dependendo do pacote).

- Suporte a tensões de 1,5 V, 1,8 V, 2,5 V e 3,3 V.

- Tolerância parcial a 5 V.

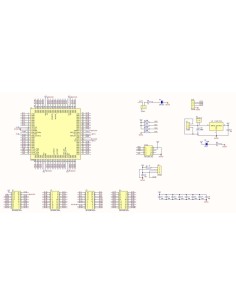

- Pacotes disponíveis: VQFP‑44, QFN‑48, CP‑BGA‑56, VQFP‑100.

- Programação: via JTAG IEEE 1149.1 e suporte a ISP (In‑System Programming).

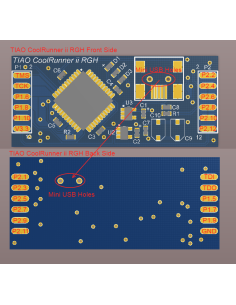

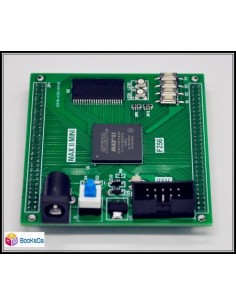

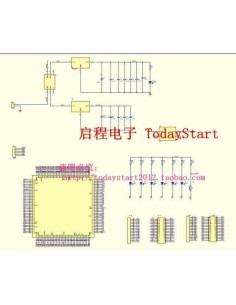

📊 Recursos da placa Matrix Glitcher CPLD

- Chip principal: Xilinx XC2C64A.

- Formato: placa compacta, geralmente usada em experimentos de glitching (injeção de falhas controladas em sinais digitais).

- Interfaces:

- Conector JTAG para gravação e debug.

- Headers de I/O para fácil conexão a outros sistemas.

- Recursos adicionais:

- Oscilador de clock embutido.

- LEDs e pinos de teste para feedback visual.

- Software compatível: Xilinx ISE WebPACK (gratuito), usado para síntese e programação.

🔹 Aplicações típicas

- Educação: aprendizado de lógica programável e CPLDs.

- Prototipagem: controle de sinais digitais, multiplexadores, decodificadores.

- Glitching controlado: usado em experimentos de segurança de hardware, injeção de falhas e testes de robustez.

- Interface simples: ideal para projetos que exigem lógica fixa e confiável com baixo consumo.

No reviews