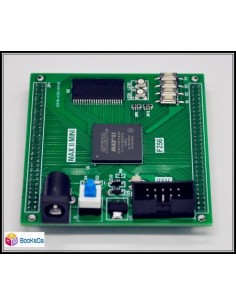

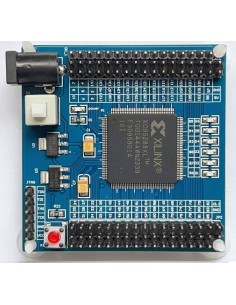

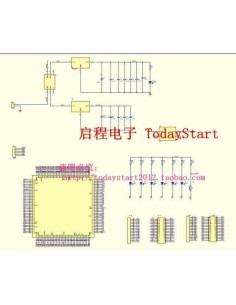

This development board is built around the Altera MAX II CPLD (EPM1270T144C5NSRA) and integrates high-speed data handling and memory resources, making it ideal for digital logic prototyping, embedded system design, and educational use.

🔹 Core Components

- CPLD: Altera MAX II EPM1270T144C5NSRA

- 1,270 macrocells

- 3.3V operation

- All I/O pins are fully routed and labeled on the silkscreen for easy access

- SRAM Memory: ISSI61LV25616-10

- 256K × 16-bit (512 KB total)

- High-speed parallel access for data buffering and logic operations

- USB Interface: CY7C68013A-56PVXC

- USB 2.0 high-speed controller

- Enables fast data transfer between board and host PC

- Acts as a bridge for CPLD programming and communication

- EEPROM: 24LC64

- 64 Kbit non-volatile memory

- Stores firmware or configuration data for the USB controller

🔹 Power and Clock

- Power Supply:

- Accepts 5V external input or USB power

- Onboard AMS1117-3.3 LDO regulator provides stable 3.3V for logic components

- Tantalum capacitors ensure clean power filtering

- Clock Source:

- 48 MHz active crystal oscillator for precise timing and synchronous logic

🔹 User Interface and Expansion

- Indicators and Controls:

- 2 programmable LEDs

- 2 push buttons for input testing or control logic

- I/O Expansion:

- All CPLD pins are broken out to headers

- Silkscreen labels for each pin simplify prototyping and debugging

🧪 Ideal Applications

- Custom processor or FSM implementation

- High-speed logic interfacing and buffering

- USB-based data acquisition or control systems

- Educational platforms for VHDL/Verilog training

- SRAM-based memory controller experiments

No reviews