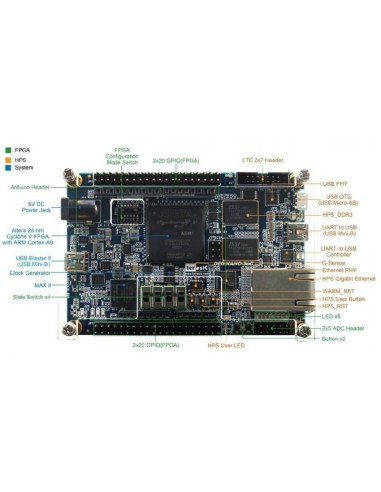

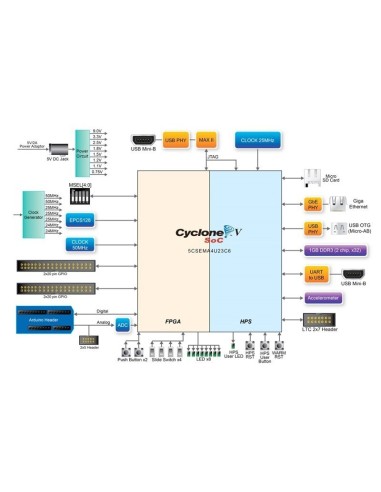

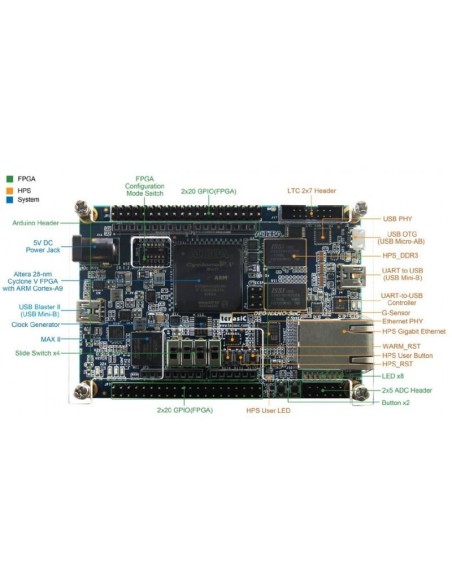

O Terasic DE0‑Nano‑SoC Kit / Atlas‑SoC Kit é uma placa de desenvolvimento baseada no Intel (Altera) Cyclone® V SE SoC FPGA – 5CSEMA4U23C6N, que combina um FPGA com um processador ARM Cortex‑A9 dual‑core. Ele é voltado tanto para desenvolvedores de hardware (DE0‑Nano‑SoC) quanto para desenvolvedores de software embarcado (Atlas‑SoC). Toda a documentação, esquemáticos, exemplos e imagens de suporte estão disponíveis nos sites da Terasic e da comunidade RocketBoards.

⚙️ Descrição técnica – DE0‑Nano‑SoC / Atlas‑SoC

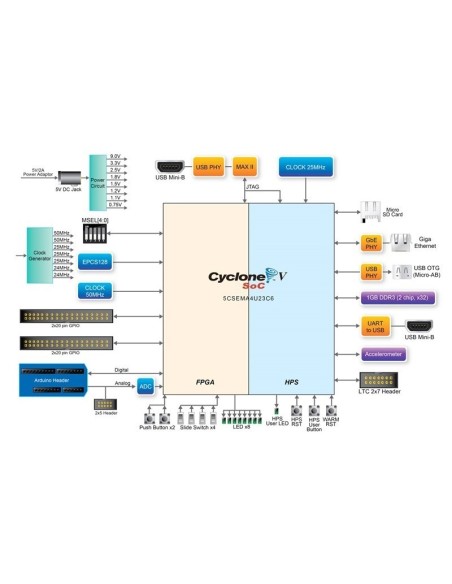

- FPGA principal: Cyclone® V SE SoC (5CSEMA4U23C6N)

- ~40K elementos lógicos

- 2.460 Kbits de memória embutida

- Controladores de memória hard

- PLLs fracionais

- Processador HPS: ARM Cortex‑A9 dual‑core @ 925 MHz

- Controladores DDR3, periféricos integrados, interconexão de alta largura de banda com FPGA.

- Memória:

- 1 GB DDR3 SDRAM (32‑bit bus)

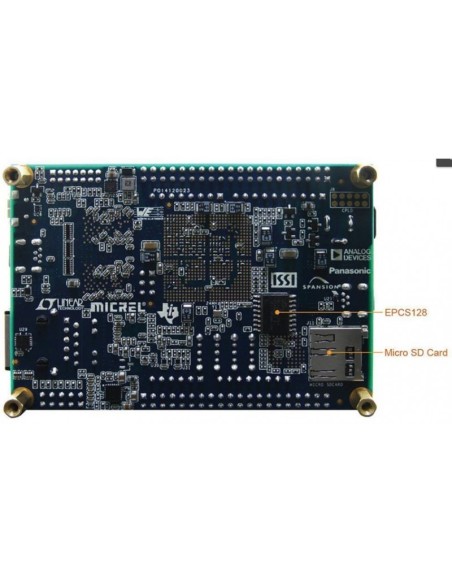

- Flash EPCS128 para configuração

- MicroSD card socket (vem com cartão de 4 GB pré‑instalado em alguns kits).

- Interfaces e periféricos:

- Gigabit Ethernet RJ45

- USB OTG (micro‑AB)

- UART‑to‑USB (mini‑B)

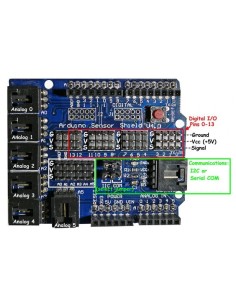

- Arduino UNO R3 header (compatível com shields)

- Dois headers de 40 pinos GPIO

- Header analógico de 10 pinos (ADC 8 canais, 12 bits, 500 ksps)

- Acelerômetro integrado (I²C + interrupção)

- Recursos de usuário:

- 8 LEDs, 4 switches, 2 push‑buttons

- Botões de reset (warm e cold reset)

- Osciladores de 50 MHz (três fontes de clock).

No reviews