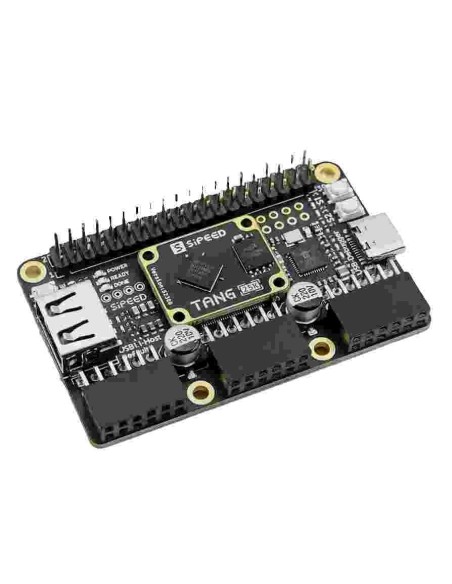

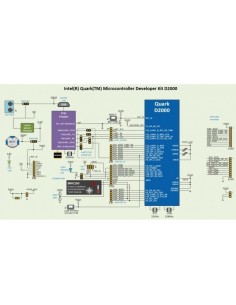

Tang Primer 25K (FPGA Gowin GW5A‑25)

A Tang Primer 25K é uma placa de desenvolvimento FPGA avançada da Sipeed, baseada no poderoso Gowin GW5A‑25, oferecendo alta capacidade lógica, recursos modernos e excelente desempenho para aplicações embarcadas, computação paralela, aprendizado de FPGA e projetos profissionais.

Combinando 25K LUTs, memória embutida, blocos DSP, interfaces de alta velocidade e conectividade flexível, a Tang Primer 25K é ideal para quem deseja explorar FPGA de última geração em um formato compacto e acessível.

✅ Características Principais

- FPGA: Gowin GW5A‑25

- LUTs: ~25.000

- Memória interna: BRAM integrada

- DSPs: Blocos DSP para operações matemáticas e processamento de sinais

- Clock: Oscilador integrado + entrada externa

- Programação: Via USB‑C (programador integrado)

- Memória externa: SDRAM / PSRAM (dependendo da versão)

- Interfaces disponíveis:

- GPIOs de uso geral

- Conectores de expansão

- Interfaces de alta velocidade (dependendo da placa)

- Alimentação: 5 V via USB‑C

- Formato compacto e ideal para prototipagem

✅ Recursos de Desenvolvimento

- Suporte completo ao Gowin IDE (gratuito)

- Compatível com Verilog, VHDL e SystemVerilog

- Ferramentas integradas de síntese, place‑and‑route e simulação

- Exemplos e bibliotecas fornecidos pela comunidade Sipeed

- Ideal para aprendizado, ensino e desenvolvimento profissional

✅ Aplicações

- Lógica digital avançada

- Processamento de sinais (DSP)

- Sistemas embarcados personalizados

- Interfaces de alta velocidade

- Prototipagem de hardware

- Computação paralela

- Desenvolvimento de SoCs softcore (como RISC‑V)

- Projetos educacionais e acadêmicos