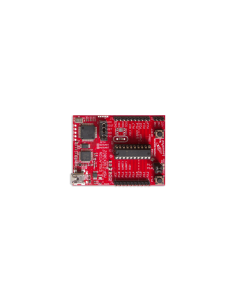

O Sipeed RV-Debugger Plus JTAG+UART é um depurador open-source baseado no chip Bouffalo Lab BL702 (RISC-V). Ele funciona como uma interface JTAG + UART via USB, permitindo programação, depuração e comunicação serial com microcontroladores e SoCs RISC-V.

📊 Descrição detalhada

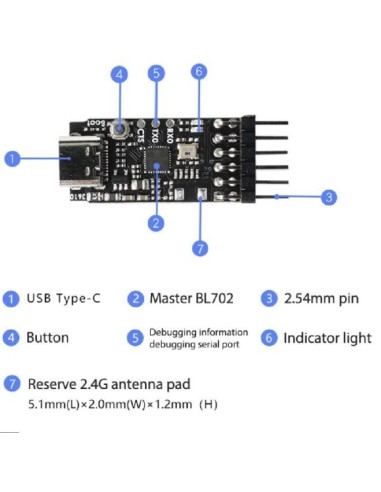

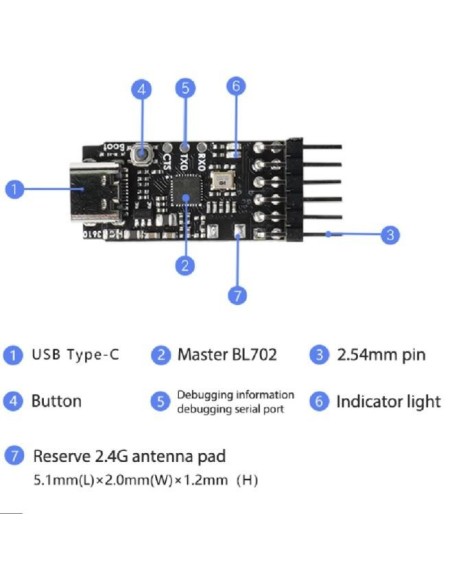

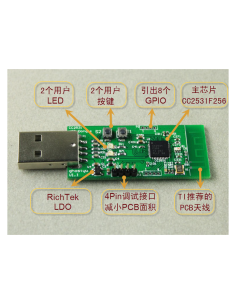

🔹 Hardware

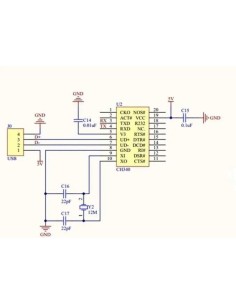

- Chip principal: Bouffalo Lab BL702C-A0 (RISC-V, até 144 MHz, com BLE/Zigbee integrados)

- Memória interna: 132 KB RAM, 192 KB ROM, 512 KB Flash embutida

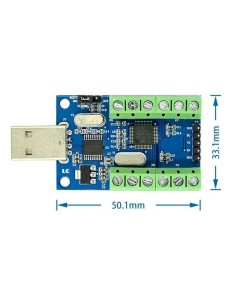

- Interface USB: USB 2.0 Full-Speed, emulação de dispositivo FT2232D

- Conectores:

- UART: pinos Tx/Rx dedicados (conector de 12 pinos)

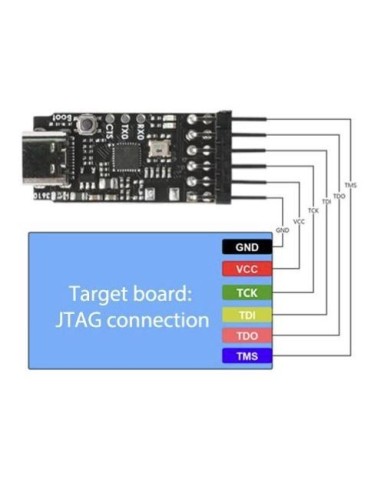

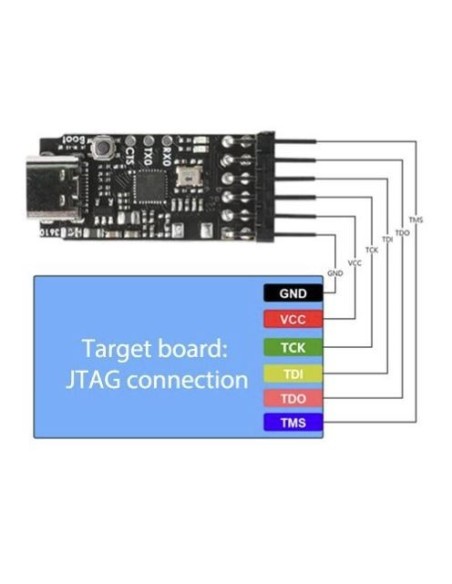

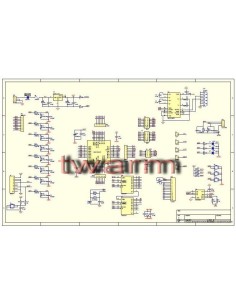

- JTAG: 8 sinais para depuração

- Alimentação: barras de 5V e 3,3V disponíveis

- Conector USB-C para ligação ao PC

🔹 Funcionalidades

- Depuração JTAG: suporte a depuração em tempo real de CPUs RISC-V.

- Comunicação UART: interface serial para logs, bootloaders e comunicação com firmware.

- ISP/IAP: programação direta via USB sem necessidade de gravador externo.

- Emulação FT2232D: compatível com ferramentas que usam FTDI para JTAG/UART.

- Firmware flexível: pode ser configurado como JTAG+UART, dual-UART ou até debugger Bluetooth.

- Compatibilidade: funciona em Windows, Linux e macOS.

🔹 Uso típico

- Programar e depurar placas com RISC-V (ex.: Sipeed, Bouffalo, Gowin FPGA).

- Comunicação serial com microcontroladores durante desenvolvimento.

- Ferramenta barata e compacta para substituir depuradores FTDI/JTAG tradicionais.

No reviews